用分立組件設計穩健的串聯線性穩壓器 |

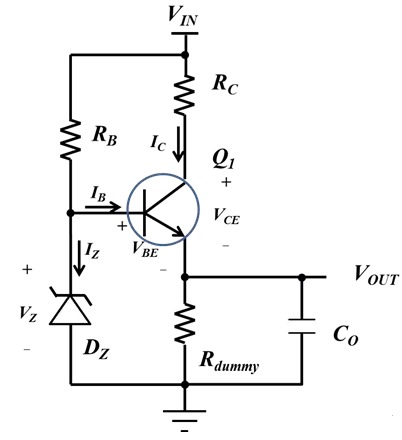

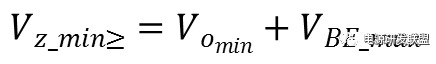

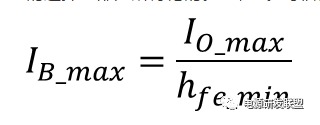

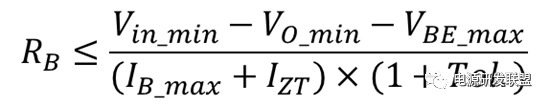

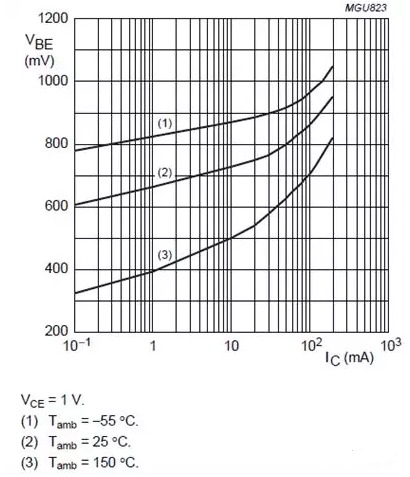

有些應用需要寬松的輸出調節功能以及不到20mA的電流。對這樣的應用來說,采用分立組件打造的線性穩壓器是一種低成本高效益的解決方案(圖1)。而對于具有嚴格的輸出調節功能并需要更大電流的應用,則可使用高性能的低壓差線性穩壓器(LDO)。 有兩個與圖1所示電路相關的設計挑戰。第一個挑戰是要調節輸出電壓,第二個挑戰是要在短路事件中安然無恙。本文將討論如何用分立組件設計穩健的線性穩壓器。 下面是一個用來給微控制器供電的示例: 輸入范圍:8.4V至12.6V 輸出范圍:1.71V至3.7V 較大負載電流:Io_max = 20mA 1.雙極型NPN晶體管的選擇 NPN雙極型晶體管Q1是重要的組件。筆者首先選擇了這種器件。 該晶體管應符合下列要求: ① 集電極至發射極和基極至發射極的擊穿電壓應超過較高輸入電壓Vin_max。 ② 集電極較大允許電流應超過較大負載電流Io_max。 除了這兩項基本要求之外,使用具有備選封裝的組件也是一個好主意。當涉及到功耗時,擁有這種靈活性將會簡化以后的設計過程。筆者為這種應用選擇了具有備選封裝和不同額定功率的NPN晶體管。 下面是筆者所用NPN晶體管的關鍵特性。 當IC = 50mA時: 直流(DC)電流增益hFE = 60; 集電極-發射極較高飽和電壓VCEsat = 300mV; 基極-發射極較高飽和電壓VBEsat = 950mV。 2.齊納二極管Dz的選擇 輸出電壓等于反向齊納電壓VZ減去該晶體管基極至發射極電壓VBE。因此,較低反向齊納電壓應符合下述要求(方程式1):  對于這種應用,筆者選用的一個測試條件是IZT = 1mA,并選擇了一個具有以下特性的齊納二極管: 當Vo_min = 1.71V且VBE_max= 0.95V時,Vz_min應大于2.65V。 當反向電流IZT = 1mA時,較低反向電壓VZ_min = 2.7V。 當反向電流IZT = 5mA時,較高反向電壓VZ_max = 3.8V。 3.基極上拉電阻器RB 電阻器RB可為齊納二極管和晶體管基極提供電流。在運行條件下,它應提供足夠的電流。齊納二極管反向電流IZ應大于1mA,正如筆者在“齊納二極管Dz的選擇”部分所討論的。方程式2可估算出運行所需的較大基極電流:  其中Hfe_min = 60。因此,IB_max ≈ 0.333mA。 方程式3可計算出RB的值。筆者使用了一個具有1%容差的電阻器。  故此,RB應小于4.26kΩ。筆者使用了一個具有4.22kΩ標準值的電阻器。 4.添加一個輸出調節的虛擬負載電阻 當負載電流為零時,輸出電壓達到較大值。當1mA ≤ IZT ≤ 5mA時,VZ較大值為3.8。VBE(on)應大于0.1V,這樣該穩壓器的輸出就能符合要求。此外,筆者還添加了一個虛擬負載電阻器,以便在無負載條件下汲取集電極電流。 圖2顯示,VBE(on)可作為集電極電流IC的函數。當IC = 0.1mA時,VBE(on) 大于0.3V。 圖2:基極-發射極導通電壓與集電極電流 方程式4可計算出該虛擬電阻:  筆者將一個36kΩ的電阻器添加到了該電路,如圖3所示。  圖3:具有虛擬負載電阻器的串聯穩壓器 5.為短路事件進行的電流限制 圖3所示電路的輸出對地短路將產生較大的集電極電流。一項PSPICE仿真結果表明,集電極電流可高達190mA,見圖4。  圖4:短路仿真結果 晶體管Q1的功耗是2.4W。沒有能應對該功耗的封裝。 為了限制短路電流,筆者添加了一個電阻器RC(從VIN到晶體管Q1的集電極),如圖5所示。  圖5:具有限流電阻器的串聯穩壓器 電阻器RC將會滿足輸出調節要求,并能在短路事件中耗散功率。筆者可計算出RC的值: VCE_Test是圖1中所用的集電極-發射極電壓。筆者為RC選擇了一個5%容差的電阻器。采用方程式5,RC應小于271Ω。使用這個估計值,在短路事件中方程式6可計算出較壞情況下的RC功耗: 該功耗約為0.56W。筆者選擇了一個1W、270Ω的功率電阻器。對于RC短路功耗更高的應用,您可把多個電阻器串聯以分擔功耗。 6.組件應力分析 就電阻器RC而言,在具有較大輸入的短路事件中會發生較壞情況下的功耗。采用方程式6,可計算出較大功耗為0.59W。 就晶體管Q1而言,因為有限流電阻器RC,所以在短路事件中不會發生較壞情況下的功耗。在正常運行期間Q1的功耗是集電極電流的函數,如方程式7所示: 當滿足下列條件時,會發生較壞的情況: VIN = VIN_max VO = VO_min IC = (VIN_max – VO_min)/(2×RC) 因此,Q1的較大功耗為(VIN_max – VO_min)2/(4×RC)。在本示例中,它是110mW。筆者選擇了一種額定功率為350mW、采用SOT23封裝的小外形晶體管。 至于RB的較大功耗,在具有較大輸入的短路事件中會發生較壞的情況。跨RB的電壓等于輸入電壓減去VBE(sat)。較大功耗估計為38mW。

文章轉載自網絡,如有侵權,請聯系刪除。 |

| | 發布時間:2018.06.16 來源:電源適配器廠家 |

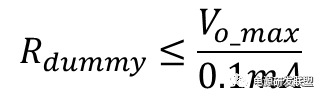

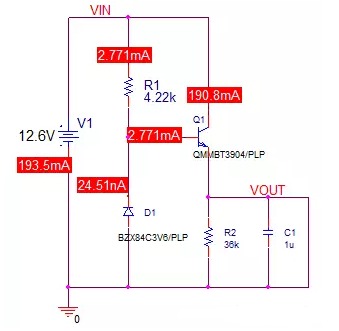

| 上一個:介紹和分析《模電》課程 | 下一個:反激式電源適配器設計詳解 |

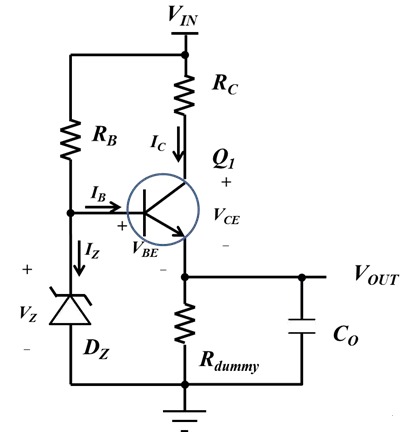

東莞市玖琪實業有限公司專業生產:電源適配器、充電器、LED驅動電源、車載充電器、開關電源等....